底部填充工艺:先进封装可靠性的关键工艺

发布时间:2025-12-20 13:52:55 浏览:1339次 责任编辑:腾盛精密

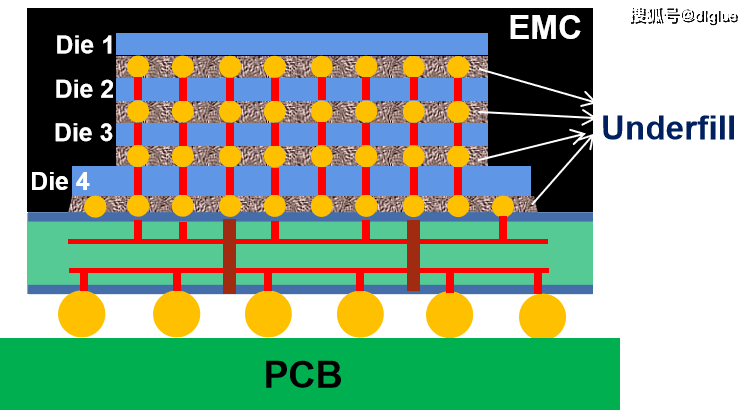

在半导体封装技术飞速发展的今天,底部填充工艺已成为确保芯片长期可靠性的核心技术之一。随着芯片集成度不断提升、封装尺寸持续缩小,热膨胀系数(CTE)失配导致的应力问题日益突出,底部填充工艺应运而生并不断发展,成为先进封装技术中不可或缺的关键环节。

▲底部填充工艺示意图 来源:网络工艺背景与发展现状

▲底部填充工艺示意图 来源:网络工艺背景与发展现状

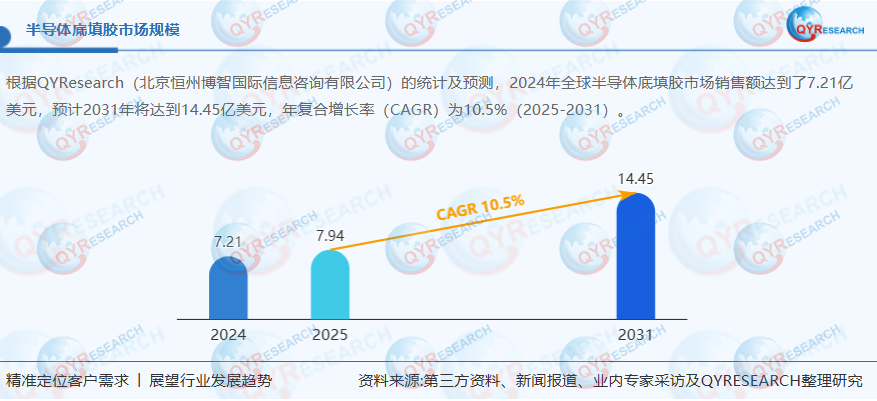

半导体底部填充技术起源于20世纪70年代的IBM公司,最初应用于陶瓷基板领域,后随着有机基板取代陶瓷基板而实现规模化应用。全球半导体底部填充胶市场预计以10.48%的年复合增长率(CAGR)持续扩张,2024年市场规模达7.21亿美元,2031年将突破14.43亿美元。中国市场表现尤为突出,预计2031年全球占比将达24.72%,增速显著高于全球平均水平,这主要得益于新能源汽车、AI芯片、5G通信等新兴技术领域的快速发展。

▲全球半导体底部填充销售额 来源:网络工艺原理与核心价值

▲全球半导体底部填充销售额 来源:网络工艺原理与核心价值

底部填充工艺的核心原理是通过在芯片与基板之间填充高分子材料,形成机械支撑结构,有效分散因热膨胀系数差异产生的应力。具体而言,当芯片与基板经历温度变化时,固化后的底部填充材料将两者紧密连接,使原本集中在焊点上的应力重新分布到整个界面区域,从而显著降低焊点所承受的应变。

底部填充工艺提供三大核心价值:

· 应力缓冲与分散:缓解CTE失配导致热机械应力,防止焊点疲劳开裂

· 增强机械强度:为焊点提供额外支撑,提高抗冲击、抗振动能力

· 环境防护:形成密封屏障,防止湿气和污染物侵入,避免腐蚀和短路

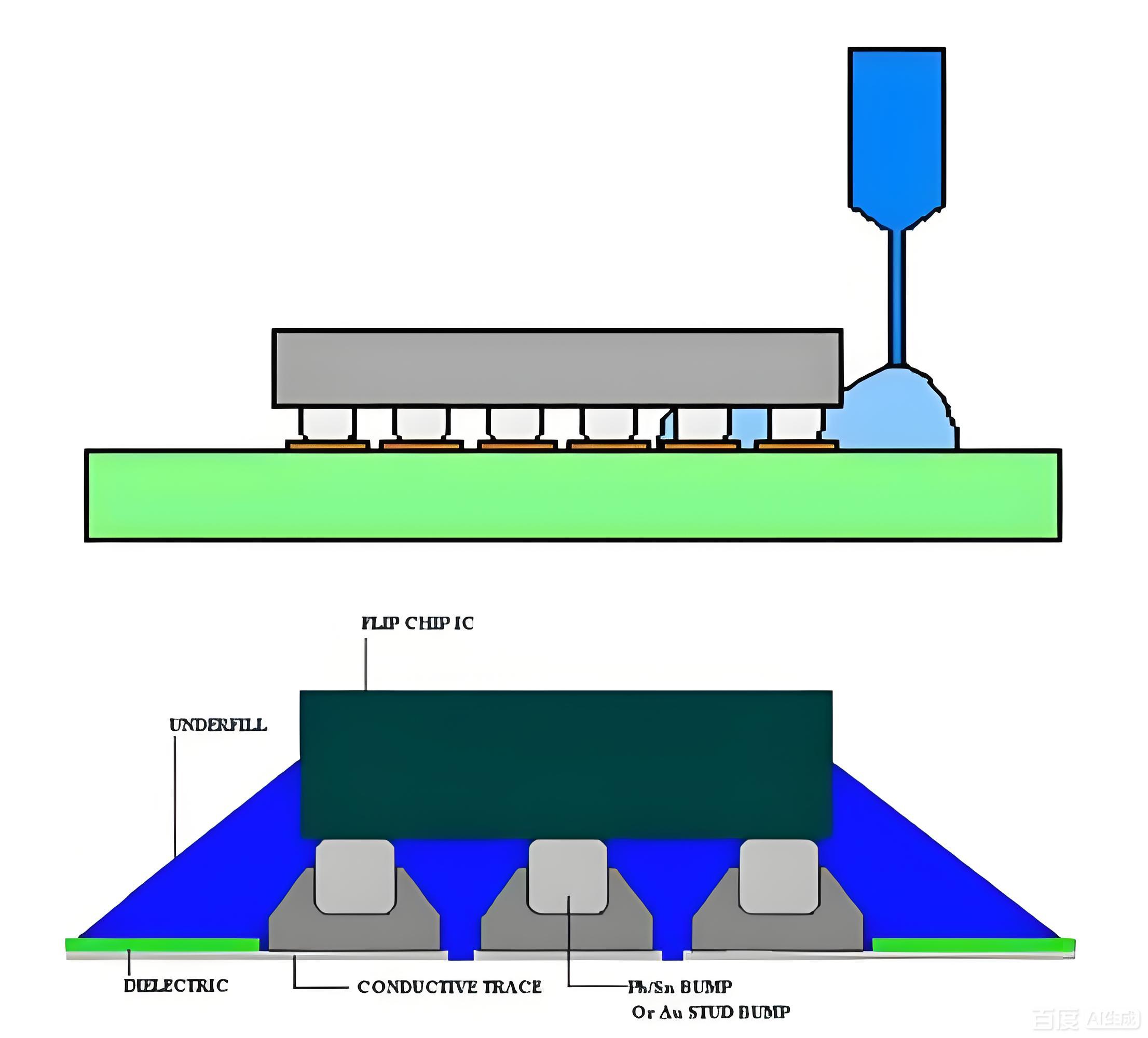

▲底部填充工艺示意图 来源:网络工艺类型与技术分类

底部填充工艺主要分为以下几类:

1. 按填充方式分类

· 毛细流动型底部填充(CUF):依赖胶水毛细流动自然填充,工艺简单但耗时较长

· 非流动型底部填充(NUF):预先点胶后通过回流焊固化,适用于CSP、BGA等工艺

· 晶圆级底部填充(WLUF):在晶圆制造阶段完成填充,适合超薄芯片

· 模塑底部填充(MUF):结合注塑成型工艺,适用于多芯片集成封装

▲底部填充工艺分类 来源:网络

2. 按应用场景分类

· 倒装芯片底部填充:用于芯片与封装基板互连凸点之间间隙的填充,精度要求高(微米级)

· BGA底部填充:用于封装基板与PCB印制电路板之间互连的焊球之间的填充,精度要求相对较低(毫米级)腾盛精密底部填充解决方案

底部填充工艺作为半导体封装中的关键环节,虽然能显著提升器件可靠性,但在实际应用中仍面临多重技术挑战,主要包括填充不饱满、空洞形成、材料匹配、热管理、大尺寸芯片封装等核心难点。作为国内领先的精密装备企业,腾盛精密针对不同封装需求开发了专业化的底部填充设备:

1、晶圆级底部填充WDS2500

· 技术特点:定制专属的设备前端模块,1供2的配置与2台点胶机组成完整系统

· 兼容性:可兼容8/12英寸晶圆,设有预热平台和冷却平台

· 应用场景:专为晶圆级Underfill工艺研发,适用于CoWoS等先进封装技术

2. 面板级底部填充Sherpa1000

·技术特点:专为面板级工艺研发,支持大面积模塑

·核心优势:可实现2-3倍的产能提升,有效缓解AI芯片对先进封装产能的瓶颈

·应用场景:适用于CoPoS等先进封装技术,满足高密度、大面积封装需求

3. 板级底部填充Sherpa900

· 技术特点:采用一体式铸造成型工艺,搭载龙门双驱U型直线电机,点胶快准稳

· 核心优势:支持选配倾斜旋转机构,实现芯片四边的倾斜点胶,对于提升Fillet,减小KOZ效果显著

· 应用场景:适用于FCBGA、FCCSP、SiP等封装中的倒装技术

在半导体产业向高性能、小型化、高可靠性发展的今天,底部填充工艺作为封装可靠性的关键保障,其技术进步将直接影响半导体产品的性能与寿命。随着中国企业在Chiplet封装等领域的持续突破,本土品牌在全球高端市场的份额有望逐步提升,为半导体产业链的自主可控发展提供有力支撑。

深圳市腾盛精密装备股份有限公司

深圳市腾盛精密装备股份有限公司